## The Signal Board Fault Detection based on BMA2000

# Guishui Yu<sup>a</sup>, Yanping Tian

School of Electronic Engineering, Naval University of Engineering, Wuhan 430033, China <sup>a</sup>yuqueishuei@aLiyun.com

**Keywords:** fault detection, signal board.

**Abstract.** This article introduces the method of expert system fault diagnosis into practice through the theoretical research of fault detection. Through research and demonstration, a fault detector is developed to make the PCB testing, as well as universal, automation, standardization and other aspects of active exploration, and to a certain type of trigger circuit boards as a signal board, to verify the corresponding algorithms and theory.

#### Introduction

A system or circuit design or manufacturing process as well as during operation need to be tested to verify if it meets the design requirements or can work. For digital system, it is mainly to test its function, time sequence and logical relations. If only to test whether there is a circuit or system failure, called fault detection; if only to check if there is a fault in the circuit or system, and to locate the point of failure, called fault diagnosis. Generally fault detection and fault diagnosis are collectively referred to as test. Here we mainly study function test.

The basic idea of fault automatic test and diagnosis is the black box theory, namely the measured object is a "mysterious" and a "black box ", in the not allowed to open the "black box " but wants to know the "black box ", only applies to a series of incentive, and then according to the response of the output response to analysis and "guess" "secrets" of the "black box".

The tester must complete four work:

Send test excitation signal to the measured object (test vector);

Receive the response under the corresponding incentive object information;

Analysis and "decision-making" an excitation vector based on the relationship between the excitation and response;

According to the excitation sequence and response sequence to determine the type and location of the fault.

It is mainly to study the function test of the PCB fault detection. Testing the function of the PCB board or system, namely checks the system timing relationships and logical correctness of the design. Logic test process is determined in advance by each input step predetermined test vector sequence, and then the response sequence of the response comparison with a predetermined standards, to determine whether the system is normal.

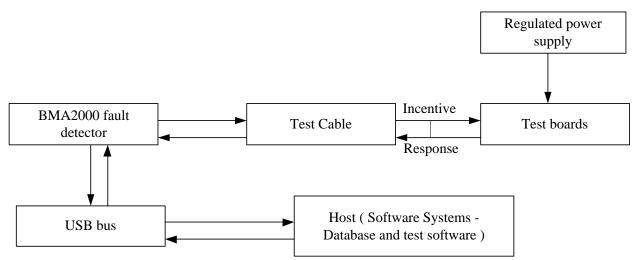

**The overall technical program.** The system overall block diagram of the fault detection technical solution based on BMA2000 the following:

BMA2000 fault tester: mainly for the circuit being measured applying energized (test vector) signal, and send the response signal to the host board. Internal is mainly composed of 16 bit single chip and Flash memory, and the data communication between the hosts by USB bus.

Host software system: internal database system is established, and the database constitutes the expert system of fault diagnosis. With excitation signal and receiving the response signal tester, according to the expert system, determine the response signal is correct or not, thus fault diagnosis is given.

**Fault testing program.** Here we are on the circuit board off-line test, this test with online testing capabilities. In the test program, we should consider the impact of the external circuit for testing.

Trigger circuit is mainly formed by the trigger circuit, charge control circuit, thyristor excitation circuit, time delay circuit, etc.

Fig. 1 The overall program of Fault detectio

The main function of the trigger circuit board. Determine the repetition frequency of rade generate driving pulse which is sent to the charge of the modulator pulse, SCR discharge switch drive pulse (i.e., the discharge pulse) and sent to the display of the trigger pulse.

Receive the monitor control, change the working state of the radar, such as wait/launch, long/short pulse conversion, etc.

**Trigger pulse forming circuit.** Oscillator: trigger circuit board within two oscillators, which are 2.6k Hz frequency pulse repetition frequency oscillator and frequency of 40Hz pendent frequency oscillator.

Divider: there are two dividers by U4-B and U4-A composition, U4 is a CMOS integrated dual D flip-flop 4013, D flip-flops here constitute two levels frequency divider circuits.

By analysis of the above works, it is easy to see the relationship between the timing logic trigger circuit board is not very complicated. It can be divided into "wait" state, the timing relationship "launch "state, long pulse and short pulse at work.

Long pulse: According to the principle of long-pulse work, the timing relationship between the signal in this mode can be expressed as follows:

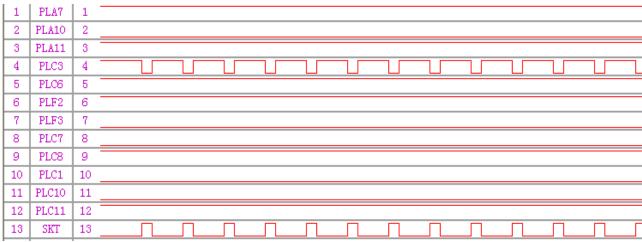

Fig.2 Long pulse timing diagram

Long pulse and short pulse period and pulse width calculation:

According to the working principle of the divider can be analyzed when a short pulse, high level account for 75% of the cycle, low level account for 25% of the cycle, the duty ratio is 3:1.In the state of long pulse, high level account for 12.5% of the cycle, low level account for 87.5% of the cycle, the duty ratio is 7:1. And a negative square wave clock pulse width is the width of 2.6 KHz, namely  $t = 1/2 \times 1/2600 \approx 192 \mu s$ . And wait for the pulse and the trigger pulse on the time difference betwe192 $\mu s$ .

Here we test the 360 beats. Test the connection as shown.

Fig.3 The test connection diagram

Get the standard test lifeforms after entering the UDT, open Triger Board subtests file, click the "Test" button to run; get the output signal waveform, click the "Replace" button to replace the expected lifeforms measured waveform. This waveform as the standard waveform, namely as a test basis, while the standard waveform stored in the database. Waveform as shown:

|     |       |    | 0<br> | 5<br>i i l | <br>10<br> | <br>15<br> | 11 | 20<br>1   1 | <br>25<br>    1 | 3 | 0<br>[ ] ] ] | 35<br>i l | 111 | 40<br> | <br>45<br>    1-1 | 50<br>1 1 1 | )<br> | 55<br> | 60<br>i l i | 11 | 65<br>i l i | 1 | 70<br> | 78<br>1 1 1 | 5<br> | 80<br>1   1 | 8 | 5<br> | ⊕(    | 0                             | Q |

|-----|-------|----|-------|------------|------------|------------|----|-------------|-----------------|---|--------------|-----------|-----|--------|-------------------|-------------|-------|--------|-------------|----|-------------|---|--------|-------------|-------|-------------|---|-------|-------|-------------------------------|---|

| 1   | PLA7  | 1  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | -     | ъ                             |   |

| 2   | PLA10 | 2  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | Ins   | кер                           |   |

| 3   | PLA11 | 3  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | Ι     | 0                             | N |

| 4   | PLC3  | 4  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | _     | V                             |   |

| - 5 | PLC6  | 5  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | H     | L                             | X |

| 6   | PLF2  | 6  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | 24    | $\stackrel{\sim}{\leftarrow}$ |   |

| 7   | PLF3  | 7  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | Ħ     |                               |   |

| 8   | PLC7  | 8  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | I:Exp | I:Test                        |   |

| 9   | PLC8  | 9  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       |       |                               |   |

| 10  | PLC1  | 10 |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       | +     | +                             |   |

| 11  | PLC10 | 11 |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       |       |                               |   |

| 12  | PLC11 | 12 |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       |       |                               |   |

| 13  | SKT   | 13 |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             | H  |             |   |        |             |       |             |   |       |       |                               |   |

| 14  |       | 0  |       |            |            |            |    |             |                 |   |              |           |     |        |                   |             |       |        |             |    |             |   |        |             |       |             |   |       |       |                               |   |

Fig.4 Long pulse timing diagram

If prompted to "test failed" and pay attention to combine to do further analysis to determine the measured signal. Firstly, check for tips in the test results suggest that information, and then check for operation, hardware problems of poor connections, etc., are determined after accurate, judging circuit board is faulty.

### **Summary**

By studying theoretical aspects of fault detection, fault diagnosis method of the expert system is introduced in practice. Through research and demonstration, we has developed a fault detector to make the PCB testing, as well as universal, automation, standardization and active exploration of other aspects, and to a certain type of trigger circuit board and as a test board, carries on the corresponding algorithm and validation of the theory, the research results show that the fault detector can distinguish trouble-free board and fault board.

#### References

[1] Zhengyou H, Yumei C, Qingquan Q. A study of wavelet entropy theory and its application in electric power system fault detection[J]. Proceedings of the CSEE, 2005, 25(5): p. 38-43.

- [2] He Z, Wu X, Qian Q. Automatic fault detection for power system using wavelet singular entropy[C]//Intelligent Mechatronics and Automation, 2004. Proceedings. 2004 International Conference on. IEEE, 2004: p. 433-437.

- [3] Huang J, Hu X, Geng X. An intelligent fault diagnosis method of high voltage circuit breaker based on improved EMD energy entropy and multi-class support vector machine[J]. Electric Power Systems Research, 2011, 81(2): p. 400-407.