# Graphene Field-effect Transistor Modeling Based on Artificial Neural Network

Guojian Cheng School of Computer Science Xi'an Shiyou University Xi'an 710065, China gjcheng@xsyu.edu.cn

Haiyang Wu\*

School of Computer Science

Xi'an Shiyou University

Xi'an 710065, China

hywu.xsyu@outlook.com

Xinjian Qiang School of Computer Science Xi'an Shiyou University Xi'an 710065, China qiangxj@xsyu.edu.cn

Abstract—Simulations and verifications on graphene electronic devices are foundations for application of graphene in integrated circuits. Modeling on graphene metal-oxide-semiconductor field-effect transistor is implemented with artificial neural network. The proposed model has high accuracy and high efficiency. The computational time for the MOSFET model is decreased significantly. More importantly, the novel model for graphene MOSFET is realized in HSPICE software as a subcircuit, which may obviously increase the efficiency of simulations on graphene large scale integrated circuits.

Keywords-graphene; field-effect transistors; modeling; artificial neural network; HSPICE

# I. INTRODUCTION

With the rapid development of the semiconductor industry, the feature size of the metal-oxide-semiconductor field-effect transistors (MOSFET) has been scaled down seriously. Traditional silicon transistors may reach their physical limits in next 10 years. A great deal of effort has focused on novel materials to substitute silicon material in preparing transistors [1-3]. Due to the outstanding electrical characteristics of graphene, such as high electron mobility and modulating band gap by changing its width [4], extensive studies on grapheme FETs have been realized and graphene FETs with different device structures are prepared. Top -gated and back-gated graphene FETs have been successfully fabricated recently [5-9]. Channels in these FETs are formed with single-layer or double-layer grapheme [10-12]. More importantly, graphene FET based circuits and blocks, for example frequency multipliers, signal mixers and amplifier have been demonstrated [13-15]. These explorations promote studies on graphene integrated circuits.

Qianyu Ji School of Computer Science Xi'an Shiyou University Xi'an 710065, China 531668715@qq.com

Qianqian Zhao School of Computer Science Xi'an Shiyou University Xi'an 710065, China 297311991@qq.com

Model for the graphene FET is the foundation of predicting performances of designed graphene circuits in different environments. Most early researches on the model of graphene FET are realized with the nonequilibrium Green's function method [16-19]. In these studies, the current-voltage (I-V) characteristics for the graphene FETs in special device structure are calculated. However, these calculations consume a lot of time and the obtained I-V characteristics can't be applied to simulate the performances of graphene FETs. Based on the measured I-V characteristics, physical models for graphene FETs are developed [20-24]. Although detailed physical models have high accuracy in simulations, one limitation of these models is the excessive demanding from a computational point of view. Artificial neural network (ANN) is a powerful tool to simulate nonlinear systems. Especially, ANN has been successfully applied to simulation carbon nanotube (CNT) FETs and nanoscale CMOS circuits [25, 26].

In this paper, model for top-gate graphene FET is put forward based on the artificial neural network. The proposed model has a high accuracy and the advantage of low time consuming. Finally, the model for the graphene FET is realized in HSPICE package as a subcircuit. These explorations may promote studies on the graphene integrated circuits.

## II. MODEL AND METHOD

# A. Model for I-V characteristics of graphene FET

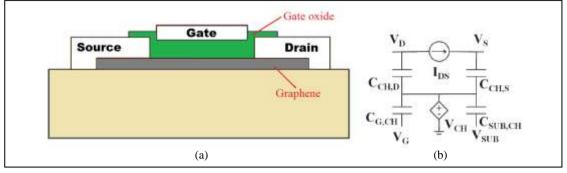

Duo to the compatibility in fabrications of top-gated graphene FETs and the existing traditional silicon CMOS technology, preparations of graphene FETs in this structure have attracted extensive studies. The schematic diagram of a typical top-gate graphene FET is present in

Fig .1 (a), in which the channel is formed by single-layer graphene. In essence, the graphene FET is a voltage controlled current source and can be modeled by the circuit in Fig .1 (b). In this model,  $V_{CH}$  is the potential of

the channel,  $I_{DS}$  indicates the current follows through the channel, capacitors  $C_{CH,S}$ ,  $C_{SUB,CH}$ ,  $C_{CH,G}$  and  $C_{CH,D}$  are used to model the transient current from the charging and discharging of the channel.

Figure 1. Schematic diagram of top-gated graphene FET (a) and circuit model (b).

$Q_{CH}$  and  $Q_{CAP}$  are the channel charge and the charge across all capacitors coupled to the channel. The two charges are functions of channel potential  $\psi_{CH}$  and their magnitudes are equal. By equating  $Q_{CH}$  and  $Q_{CAP}$ ,  $\psi_{CH}$  can be obtained. Based on this assumption, Jie Deng *et al* developed a novel method to calculate the channel potential, which is adopted in our studies [27]. Channel charge of the FET can be calculated as

$$n_{\alpha} = \int_{0}^{\infty} f(E)D_{\alpha}(E)dE \tag{1}$$

$$f(E) = \frac{1}{1 + e^{\frac{E - E_F}{kT}}}$$

(2)

where  $n_{\alpha}$  is the electron in subband  $\varepsilon_{\alpha}$ ,  $D_{\alpha}(E)$  is the density of states (DOS) of the graphene. f(E) is the Fermi-Dirac distribution function and can be calculated by (2), in which  $E_F$  is Fermi energy and k is Boltzmann's constant.

Based on the Landauer-Buttiker formalism, the electron current is defined as

$$I_{e}(\Psi_{CH}, V_{D}, V_{S}) = \frac{2qkT}{h} \sum_{\alpha} \left[ \ln\left(1 + e^{\frac{q(\Psi_{CH} - V_{S}) - \varepsilon_{\alpha}}{kT}}\right) - \ln\left(1 + e^{\frac{q(\Psi_{CH} - V_{D}) - \varepsilon_{\alpha}}{kT}}\right) \right]$$

$$(3)$$

where  $V_D$  and  $V_S$  are the potentials for the drain and source of the graphene FET. In a N-type graphene FET  $I_D = I_e$ , while for a P-type FET,  $I_D = I_h$ , which can be calculated in the same method. Cheng et al developed a graphene FET HSPICE model package [28], which is used to simulate the I-V characteristics of the top-gated graphene FET.

#### B. Neural network computations

Due to powerful self-learning and self-adapting abilities, effective online adaptation and good noise rejection capabilities, artificial neural networks have been widely used in pattern recognition, cluster analysis, signal classification, nonlinear function fitting, etc. [29]. Back propagation (BP) neural network is one of the most widely used neural networks, which is realized with multi-layer perceptron (MLP) composed of numerous

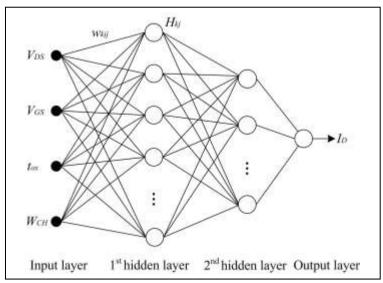

Figure 2. Schematic diagram of BP neural network with two hidden layers.

interconnected neurons. A diagram of a BP neural network with two hidden layers is shown in Fig. 2.

Neurons are basic processing elements in a BP network and connected to each other through a set of weights. In the training of the neural network, weights are adjusted based on an error-minimization method. The neural network in Fig .2 consists of four layers named as input layer, the first hidden layer, the second hidden layer and output layer. The output of neuron j in hidden layer k can be calculated as

$$H_{kj} = f(\sum_{i=1}^{h} w_{kij} X_{ki} + a_{kj}) \qquad \begin{cases} j = 1, 2, L, m \\ k = 1, 2 \end{cases}$$

(4)

Where f is the transfer function of hidden layer k, w is the weight, a is the threshold and m is the number of neurons in the hidden layer k.  $X_{1i}$  is the input of the network, and  $X_{2i}$  is the output of the first hidden layer, which is the input of the second hidden layer.

Tan-sigmoid transfer function is adopted in the two hidden layers, which has been successfully applied in simulations on the I-V characteristics of carbon nanotube FETs [25, 29, 30]. The transfer function is given by

$$f(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{5}$$

where *x* is

$$\sum_{i=1}^{h} w_{kij} X_{ki} + a_{kj}$$

in (4).

The output of the neural network is

$$I_{D} = \sum_{j=1}^{m} H_{kj} w_{j} + b \tag{6}$$

where  $H_{kj}$  is the output of neuron in the second hidden layer and b is threshold of the output layer.

The drain current  $I_D$  of a graphene FET is determined by the drain-source voltage  $V_{DS}$ , the gate-source voltage  $V_{GS}$ , gate oxide thickness  $t_{ox}$  and the channel width  $W_{CH}$ . The I-V characteristics of the graphene FET are simulated with BP neural network, in which the drain current  $I_D$  is the single output and above four parameters determining the drain current are inputs.

# III. RESULTS AND ANALYSIS

To train the neural network, about 7700 data for simulation on the I-V characteristics of the graphene FET are obtained using the HSPICE model developed by Cheng *et al.* Ranges for the inputs and output of the simulation are presented in TABLE I.

TABLE I. DATA RANGES THE I-V CHARACTERISTICS OF GRAPHENE FET

| Range |            | Outnot/u A |                     |                     |           |

|-------|------------|------------|---------------------|---------------------|-----------|

|       | $V_{DS}/V$ | $V_{GS}/V$ | t <sub>ox</sub> /nm | W <sub>CH</sub> /nm | Output/μA |

| min   | 0.0        | 0.0        | 0.5                 | 0.87                | 0.0       |

| max   | 0.5        | 0.5        | 2.5                 | 6.36                | 19.51     |

In the 7700 data for simulating the I-V characteristics of the graphene FET, about 6700 data are selected as training samples and the remaining are testing samples. To achieve appropriate neural network for simulating the graphene FET, neural networks with structure are tested and optimized, which are realized with MATLAB 2011b. Pearson's correlation coefficients between the testing samples and the predicted values from the neural network are calculated to evaluate the trained networks. Correlation coefficients for five typical neural networks are list in TABLE II. The network 4-11-9-1 has the highest correlation coefficient, which is suitable to simulate the characteristics of the graphene FET.

TABLE II. CORRELATION COEFFICIENTS FOR DIFFERENT NEURAL NETWORKS

| Networks     | 4-9-8-1 | 4-7-5-1 | 4-11-9-1 | 4-7-4-7-1 | 4-5-5-5-1 |

|--------------|---------|---------|----------|-----------|-----------|

| Coefficients | 0.99965 | 0.99964 | 0.99997  | 0.99963   | 0.99962   |

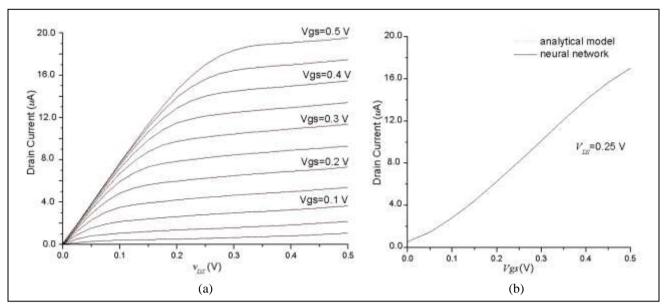

From the family of  $i_D$  versus  $v_{DS}$  curves (in Fig .3 (a)) of the n-channel graphene FET with a channel width ( $W_{CH}$ ) of 1.60 nm and a gate oxide thickness ( $t_{ox}$ ) of 0.95 nm, it can be seen that the maximum error between the prediction of the neural network and result from the analytical model is about 0.076  $\mu$ A, which is about 0.0039% of the analytical model. All relative errors in the transferring properties between the predictions of the neural network and results from the analytical model of the n-channel graphene FET are smaller than 0.0065%. Prediction values of the 4-11-9-1 neural network are suitable to simulate the I-V characteristics of the graphene FET. Similar results for p-channel graphene FET can also be obtained.

The proposed neural network model can be realized as a subcircuit in HSPICE package. In essence, the graphene FET is a voltage controlled current source. As the current between gate and source is very small and always neglected, a null current source is used to realize this approximation. The drain current can be calculated with the neural network. The general syntax for the subcircuit to simulate the graphene FET in HSPICE package is

.SUBCKT GrapheneFET Drain Gate Source

iGate Gate Source 0

iDrain Drain Source current='Drain current calculated by the neural network'

.ENDS

where "GrapheneFET" is the name of the subcircuit. "Drain", "Gate" and "Source" are the electrodes of drain, gate and source for the graphene FET.

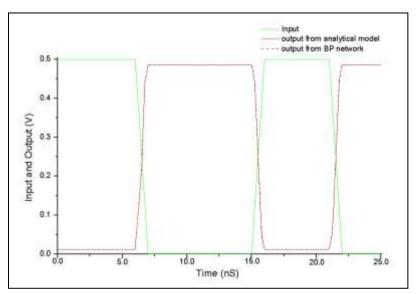

In order to validate the proposed neural network model, an inverter formed with n-channel and p-channel graphene FETs is designed. The outputs of the inverter from the analytical model and neural network model are plotted Fig .4. By comparing the outputs from the two models, it can be seen that a high similarity is achieved and the neural network model is suitable to simulate the performances of graphene circuits. It is well known that the neural network has a high efficiency in simulations on nonlinear systems. CPU time consumptions for simulations on the graphene inverter with above methods are listed in TABLE III, which are realized on a computer with an Intel I3 530 CPU and 8GB memory.

Figure 3. I-V characteristics of an n-channel graphene FET, (a) and (b) are family of  $i_D$  versus  $v_{DS}$  curves and transferring properties. Red dash line indicates data from the analytical model provided by Cheng *et al* and solid black line means by prediction of the neural network.

Figure 4. Input and output of inverter based on graphene FET. Red line indicates output from the analytical model put forward by Cheng et al and black dash line means output of the inverter of the neural network.

TABLE III. CPU TIME CONSUMPTIONS FOR SIMULATIONS ON THE OUTPUT OF THE GRAPHENE INVERTER

| Method      | analytical model | neural network |

|-------------|------------------|----------------|

| CPU time /S | 7.00             | 4.62           |

Compared with the analytical model, the proposed neural network model has a higher efficiency, which saves about 34% time of the traditional analytical model. This advantage may be more significant in large scale integrated circuit simulations. More importantly, the inputs of our proposed model can be extended to include other parameters of the graphene FET, such as temperature and the number of graphene.

# IV. CONCLUSIONS

The possibility of applying artificial neural network to modeling the I-V characteristics of the graphene FET is investigated. Data for training and optimizing the neural network are obtained from a traditional analytical model. Errors in the I-V characteristics of the FET between the analytical model and neural network are smaller than 0.0065%. The method to realize the neural network model is proposed and the performances of an inverter based on proposed model are implemented. The advantage of high efficiency for the neural network model is verified. Results in this paper may provide meaningful information on the simulation and verification for graphene integrated circuits.

# ACKNOWLEDGMENT

This work is supported by the fund of Shaanxi provincial educational department (No.2014JK1581).

## REFERENCES

Xu Weiwei, Liu Zhen, Zhao Jianwen, Xu Wenya, Gu Weibing, et al, "Flexible logic circuits based on top-gate thin film transistors

- with printed semiconductor carbon nanotubes and top electrodes," Nanoscale, Vol. 6, Dec. 2014, pp. 14891-14897, doi: 10.1039/c4nr05471g.

- [2] Fan Jiewen, Li Ming, Xu Xiaoyan, Yang Yuancheng, Xuan Haoran, et al, "Insight into gate-induced drain leakage in silicon nanowire transistors," IEEE Transactions on Electron Devices, vol. 62, Jan. 2015, pp. 213-219, doi:10.1109/TED.2014.2371916.

- [3] Standley B, Mendez A, Schmidgall E and Bockrath M., "Graphene-graphene oxide field-effect transistors," Nano Lett., vol. 12, Mar. 2012, pp. 1165-1169, doi:10.1021/nl2028415.

- [4] Jianhao Chen, Chaun Jang, Shudong Xiao, Ishigami Masa and Fuhrer Michael S., "Intrinsic and extrinsic performance limits of graphene devices on SiO<sub>2</sub>," Nature Nanotechnology, vol. 3, Mar. 2008, pp. 206-209, doi:10.1038/nnano.2008.58.

- [5] Hopf T., Vassilevski K. V., Escobedo-Cousin E., King P.J., Wright N.G., et al, "Dirac point and transconductance of top-gated graphene field-effect transistors operating at elevated temperature," Journal of Applied Physics, vol. 116, Oct. 2014, pp. 154504, doi:10.1063/1.4898562.

- [6] Francis S. Ashley, Petrosky James C., McClory John W., Cress Cory D., "Effects of proton and X-Ray irradiation on graphene field-effect transistors with thin gate dielectrics," IEEE Transactions on Nuclear Science, vol. 61, Nov. 2014, pp. 3010-3017, doi:10.1109/TNS.2014.2364780.

- [7] Feng Tingting, Xie Dan, Xu Jianlong, Zhao Haiming, Li Gang, et al, "Back-gate graphene field-effect transistors with double conductance minima," Carbon, vol. 79, Nov. 2014, pp. 363-368, doi:10.1016/j.carbon.2014.07.078.

- [8] Corbet Chris M., McClellan Connor, Kim Kyounghwan, Sonde Sushant, Tutuc Emanuel, et al, "Oxidized titanium as a gate dielectric for graphene field effect transistors and its tunneling mechanisms," ACS Nano, vol. 8, Oct. 2014, pp. 10480-10485, doi:10.1021/nn5038509.

- [9] Wang Wei, Yang Xiao, Li Na, Zhang Lu, Zhang Ting, et al, "Numerical study on the performance metrics of lightly doped drain and source graphene nanoribbon field effect transistors with double-material-gate," Superlattices and Microstructures, vol. 64, Dec. 2013, pp. 227-236, doi:10.1016/j.spmi.2013.09.032.

- [10] IIIarionov Yu Yu, Smith A D, Vaziri S, Ostling M., Mueller T., et al, "Bias-temperature instability in single-layer graphene fieldeffect transistors," Applied Physics Letters, vol. 105, Oct. 2014, pp. 143507, doi:10.1063/1.4897344.

- [11] Wang Xiaojuan, Guo Yunxian, Zhang Zengxing, "Field-effect transistors based on single graphene oxide nanoribbon from longitude-unzipped carbon nanotubes," Journal of Nanoparticle Research, vol. 15, Dec. 2013, pp. 2147, doi:10.1007/s11051-013-2147-7.

- [12] Nourbakhsh Amirhasan, Agarwal Tarun K., Klekachev Alexander, Asselberghs Inge, Cantoro Mirco, et al, "Chemically enhanced double-gate bilayer graphene field-effect transistor with neutral channel for logic applications," Nanotechnology, vol. 25, Aug. 2014, pp. 345203, doi:10.1088/0957-4484/25/34/345203.

- [13] Ramn Michael E., Parrish Kristen N., Chowdhury Sk. Fahad, Magnuson Car W., Movva Hema C. P., et al, "Three-gigahertz graphene frequency doubler on quartz operating beyond the transit frequency," IEEE Trans. Nanotechnol., vol. 11, Sep. 2012, pp. 877 -883, doi:10.1109/TNANO.2012.2203826.

- [14] Habibpour Omid, Cherednichenko Sergey, Vukusic Josip, Yhland Klas, and Stake Jan, "A subharmonic graphene FET mixer," IEEE Electron Device Letters, vol. 33, Jan. 2012, pp. 71-73, doi: 10.1109/LED.2011.2170655.

- [15] Lee Jaehong, Lee Jaeho, Seo David H., Shin Hyungcheol, Park Seongjun, et al, "Step-by-step implementation of an amplifier circuit with a graphene field-effect transistor on a printed-circuit board," Current Applied Physics, vol. 14, Aug. 2014, pp. 1057-1062, doi:10.1016/j.cap.2014.05.015.

- [16] Lewenkopf Caio H. and Mucciolo Eduardo R, "The recursive Green's function method for graphene," Journal of Computational Electronics, vol. 12, Jun. 2013, pp. 203-231, doi:10.1007/s10825-013-0458-7.

- [17] Shokri A. A. and Mosavat A. H., "Electronic transport of graphene nanoribbons within recursive Green's function," Superlattices and Microstructures, vol. 51, Apr. 2012, pp. 523-532, doi: 10.1016/j.spmi.2012.01.016.

- [18] Sarvari H. and Ghayour R., "A fast method to analyze and characterize the graphene nanoribbon FET by Non-Equilibrium Green's Function," 2010 IEEE International Conference on Semiconductor Electronics (ICSE 2010), IEEE Press, Jun. 2010, pp. 219-223, doi:10.1109/SMELEC.2010.5549561.

- [19] Chin Sai-Kong, Seah Dawei, Lam Kai-Tak, Ganesh S., and Liang Gengchiau, "Device physics and characteristics of graphene nanoribbon tunneling FETs," IEEE Transactions on Electron Devices, vol. 57, Nov. 2010, pp. 3144-3152, doi: 10.1109/TED.2010.2065809.

- [20] MacKin Charles, Hess Lucas H., Hsu Allen, Song Yi, Kong Jing, et al, "A current-voltage model for graphene electrolyte-gated field-effect transistors," IEEE Transactions on Electron Devices, vol. 61, Dec. 2014, pp. 3971-3977, doi: 10.1109/TED.2014.2360660.

- [21] Saeidmanesh M., Rahmani M., Karimi H., Khaledian M., and Ismail Razali, "Analytical model for threshold voltage of double gate bilayer graphene field effect transistors," Microelectronics Reliability, vol. 54, Jan. 2014, pp. 44-48, doi: 10.1016/j.microrel.2013.08.003.

- [22] Martin Landauer, G., Jimenez, D. and Gonzalez, J. L., "An accurate and Verilog-A compatible compact model for graphene field-effect transistors," IEEE Transactions on Nanotechnology, vol. 13, Sep. 2014, pp. 895-904, doi: 10.1109/TNANO.2014.2328782.

- [23] Lee Dongheon, Lee Kihwan, Kim Kangmin, and Kim Ohyun, "New analytical drain current model for the sub-linear region of output characteristics of graphene field-effect transistors in the low carrier density limit," Journal of Nanoscience and Nanotechnology, vol. 14, Dec. 2014, pp. 9082-9087, doi:10.1166/jnn.2014.10082.

- [24] Mousavi S. Mahdi, Ahmadi M. Taghi, Nilghaz Azadeh, Samadi Javad, Kiani M. Javad, et al, "Current-voltage characteristics of bilayer graphene nanoribbon field effect transistor," Journal of Computational and Theoretical Nanoscience, vol. 10, Mar. 2013, pp. 738-741, doi:10.1166/jctn.2013.2763.

- [25] Mohsen Hayati, Abbas Rezaei and Majid Seifi, "CNT-MOSFET modeling based on artificial neural network: Application to simulation of nanoscale circuits," Solid-State Electronics, vol. 54, Jan. 2010, pp. 52-57, doi:10.1016/j.sse.2009.09.027.

- [26] Djeffal F., Chahdi M., Benhaya A. and Hafiane, M.L., "An approach based on neural computation to simulate the nanoscale CMOS circuits: Application to the simulation of CMOS inverter," Solid-State Electronics, vol. 51, Jan. 2007, pp. 26-34, doi: 10.1016/j.sse.2006.12.004.

- [27] Deng Jie and Wong H.-S. Philip, "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application Part I: Model of the intrinsic channel region," IEEE Transactions on Electron Devices, vol. 54, Dec. 2007, pp. 3186-3194, doi:10.1109/TED.2007.909030.

- [28] Chen Ying-Yu, Rogachev Artem, Sangai Amit, Iannaccone Giuseppe, Fiori Gianluca, et al, "A SPICE-compatible model of graphene nano-ribbon field-effect transistors enabling circuit-level delay and power analysis under process variation," 16th Design, Automation and Test in Europe Conference and Exhibition (DATE 2013), IEEE Press, Mar. 2013, pp. 1789-1794, doi: 10.7873/DATE.2013.359.

- [29] Cybenko G. "Approximation by superpositions of a sigmoidal function," Mathematics of Control Signals and Systems, vol. 2, Dec. 1989, pp. 303-314, doi:10.1007/BF02551274.

- [30] Djeffal F., Dibi Z., Hafiane M. L. And Arar D., "Design and simulation of a nanoelectronic DG MOSFET current source using artificial neural networks," Materials Science and Engineering C, vol. 27, Sep. 2007, pp. 1111-1116, doi:10.1016/j.msec.2006.09.005.